时钟发生器在高性能计算系统中的作用与优化策略

时钟发生器如何支撑高性能计算系统

在高性能计算(HPC)与人工智能加速平台中,时钟发生器不仅是时间基准,更是系统并行处理能力的“神经脉搏”。其设计优劣直接影响芯片的功耗、延迟与整体吞吐量。

1. 高性能系统对时钟的要求

- 多路输出同步:支持多个时钟域同时输出,满足不同子系统需求。

- 低延迟抖动:微秒级甚至纳秒级的抖动控制,保障数据采样一致性。

- 动态频率调整:支持按需调频(DVFS),提升能效比。

2. 优化时钟发生器设计的关键策略

为了应对复杂系统挑战,工程师常采用以下优化手段:

- 使用多级锁相环架构:通过多级反馈环路提高频率稳定性和灵活性。

- 引入自适应校准算法:根据环境温度、电压变化自动修正时钟偏差。

- 采用差分时钟输出:减少电磁干扰(EMI),提升信号完整性。

- 集成监控电路:实时监测时钟状态,支持故障预警与自恢复。

3. 实际案例:AI芯片中的时钟管理

以英伟达A100 GPU为例,其内部集成了多个独立的时钟发生器模块,分别服务于计算核心、显存控制器和高速互连总线。通过精细化的时钟树设计,实现了高达1500MHz的有效主频,并将周期间抖动控制在100ps以内,显著提升了矩阵运算效率。

- 时钟发生器在高性能计算系统中的作用与优化策略

- 时钟发生器在高性能计算系统中的关键作用

- 时钟发生器在高速数字系统中的关键挑战与优化策略

- 实时时钟芯片在嵌入式系统中的核心作用与优化策略

- 深入理解时钟发生器原理及其在高性能计算中的作用

- 时钟发生器在高性能计算中的关键角色分析

- MEMS时钟发生器在高端通信与AI边缘计算中的关键作用

- 时钟发生器与时钟管理:构建高性能数字系统的基石

- 时钟信号器件在高速数字系统中的关键作用与选型策略

- 深入解析时钟发生器在高速数字系统中的关键作用

- 时钟发生器与时钟分配网络的协同设计优化

- 深入解析可编程时钟发生器在高速通信系统中的应用与优势

- 时钟发生器在嵌入式系统中的关键作用与选型建议

- 实时时钟芯片在物联网系统中的关键作用与技术优化

- 深入解析计时器与运行时间监控在系统性能优化中的关键作用

- 时钟信号器件在高性能计算中的关键角色

- 深入理解时钟发生器原理及其在嵌入式系统中的关键作用

- 计时器与计时时钟IC在现代电子系统中的核心应用解析

- 深入探讨时钟信号器件的设计挑战与优化策略

- 深入理解时钟信号器件的设计挑战与优化策略

-

深入理解接口隔离器:从理论到实践的技术演进

接口隔离器的技术演进与未来趋势随着分布式系统复杂性的增加,接口隔离器已从简单的“接口封装”演变为智能化的系统控制中心。其...

-

接口隔离器:现代系统架构中的关键角色与应用解析

接口隔离器在系统设计中的核心作用在现代软件架构中,接口隔离器(Interface Isolator)作为解耦系统组件的重要工具,正日益受到开发团...

-

时钟缓冲器与驱动器的功能差异及应用场景解析

时钟缓冲器与驱动器的核心区别在现代数字系统设计中,时钟信号的稳定性和传输质量至关重要。时钟缓冲器(Clock Buffer)和时钟驱动器...

-

工业控制微控制器的安全架构设计与发展趋势

工业控制微控制器安全架构的设计框架现代工业控制系统面临复杂多变的安全威胁,仅靠单一安全措施已不足以应对。因此,必须从系统...

-

接口芯片选型指南:如何根据项目需求选择合适的芯片方案

接口芯片选型指南:如何根据项目需求选择合适的芯片方案在嵌入式系统开发中,正确选择接口芯片是确保系统稳定运行和高效通信的重...

-

深入理解RF射频器件的关键性能指标与选型要点

RF射频器件核心性能参数解析在实际工程应用中,正确选择合适的射频器件至关重要。以下为几个关键性能指标及其影响:1. 工作频率范围...

-

RF射频器件的分类与应用:从天线到滤波器的全面解析

RF射频器件的核心组成与功能RF射频器件是无线通信系统中的关键组成部分,广泛应用于移动通信、卫星导航、雷达、物联网(IoT)及5G网...

-

振荡器:原理、应用与种类

振荡器是一种电子设备或电路,其功能是产生重复性的电压或电流信号。这些信号通常具有特定的频率和波形,是许多电子系统中的关键...

-

微控制器在现代技术中的应用与重要性

微控制器在现代技术中扮演着至关重要的角色,它们广泛应用于各种设备和系统中,从家用电器到工业控制系统,再到复杂的医疗设备。...

-

8位微控制器:特性、应用及发展趋势

8位微控制器是一种广泛应用于各种电子设备中的集成电路。它们通常用于执行控制功能,例如在家电、汽车系统、医疗设备等中。这些微...

-

湿度传感器:原理、应用与未来发展趋势

湿度传感器是一种能够感知并测量环境空气中水分含量的设备。它们广泛应用于气象学、农业、工业生产以及家庭自动化系统中,以监测...

-

时钟缓冲器、驱动器与锁相环的功能与应用

时钟缓冲器、驱动器以及锁相环是电子系统中关键的时序控制组件。时钟缓冲器的主要作用是放大和分配时钟信号,确保整个系统中的所...

-

开发套件:助力创新与实践的全面解决方案

开发套件是专为软件开发者、硬件工程师以及技术爱好者设计的一系列工具集合。它旨在简化产品的开发流程,提高工作效率,并激发创...

-

温度传感器的工作原理及应用

温度传感器是一种能够感知温度变化并将之转换为可用输出信号的装置。它们广泛应用于各种领域,如家用电器、汽车工业、医疗设备以...

-

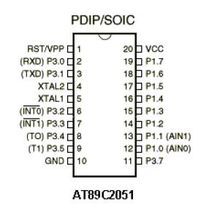

AT89C2051-24SU微控制器:中芯泰原装现货的高性能低功耗单片机

AT89C2051-24SU是一款由中芯泰公司生产的微控制器,它属于89C2051系列,是一种低功耗、高性能的单片机。这款微控制器广泛应用于各种电子...

-

PIC16F648A-I/SO微芯科技8位单片机的特性与应用

PIC16F648A-I/SO是一款由Microchip Technology(微芯科技)生产的8位微控制器,属于PIC16F系列。这款单片机以其高性能、低功耗和丰富的外设而受...

-

ATMEGA2560-16AU微控制器芯片的详细介绍

ATMEGA2560-16AU是一款由Atmel公司(现为Microchip Technology的一部分)生产的微控制器,属于AVR系列。这款芯片以其高性能和丰富的外设接口而广...

-

Silicon Labs C8051F410-GQ和C8051F411微控制器概述

C8051F410-GQ和C8051F411是Silicon Labs(以前称为Cypress Semiconductor)生产的微控制器,它们属于8051系列。这个系列的微控制器以其简单、高效和广...

-

微芯科技PIC18F23K22-I/SO微控制器详细介绍

微芯科技(Microchip Technology)是一家知名的半导体公司,专注于微控制器、混合信号、模拟器件和闪存IP解决方案。PIC18F23K22-I/SO 是微芯科...

-

C8051F340-GQR 硅基微控制器芯片的原装现货供应

C8051F340-GQR 是一款集成电路芯片,属于硅(Silicon)材料制成的微电子组件。这种芯片通常用于嵌入式系统和微控制器应用,具有高性能和...